The job listing no longer exists.

Open Positions

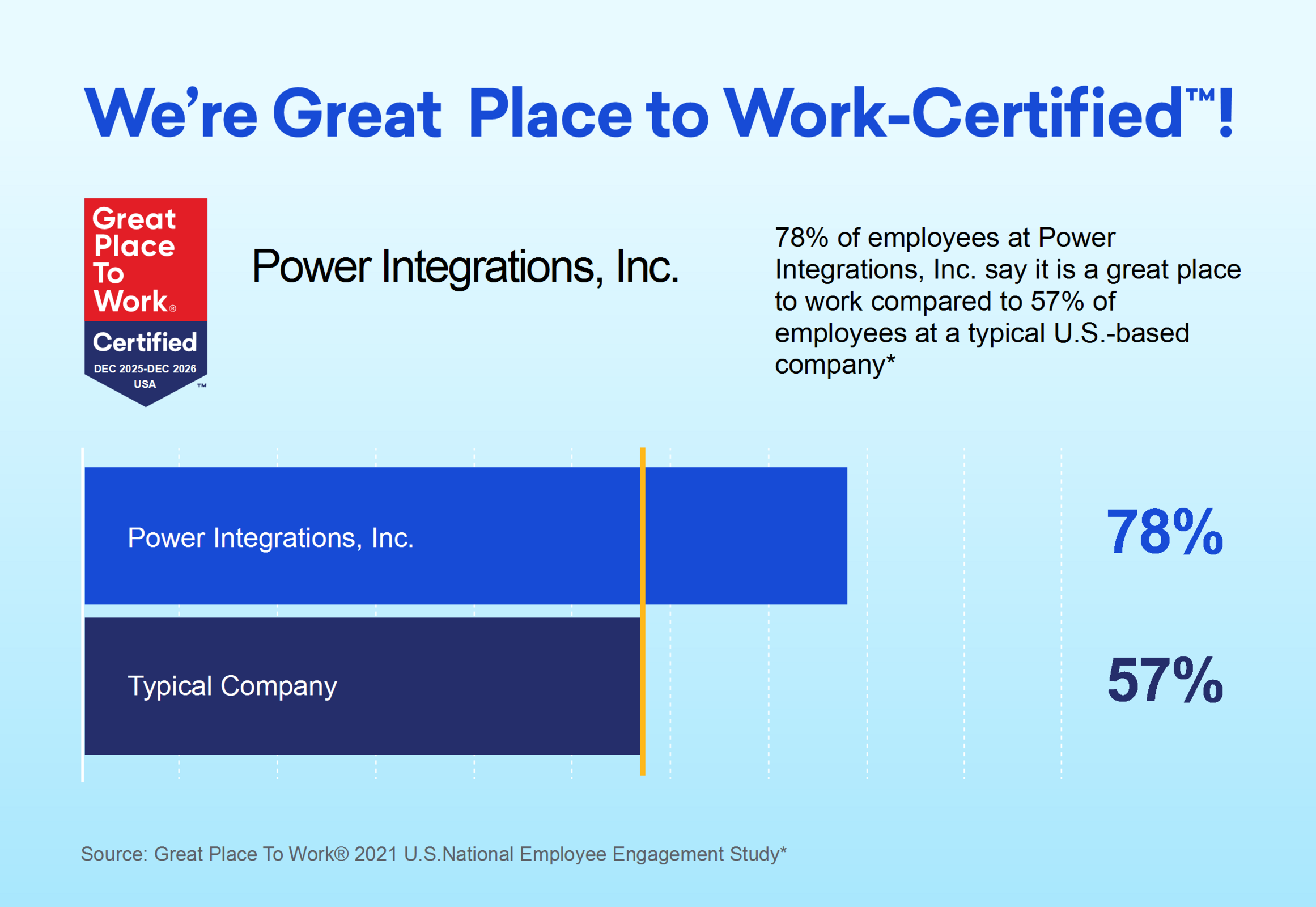

Power Integrations competes for the best talent. Our compensation packages consist of salary and equity, and they are commensurate with accomplishment. We offer a full suite of benefits.

It is the policy of Power Integrations to provide equal employment opportunity for all employment applicants and employees without regard to prohibited considerations of race, color, religion, gender, gender identity, gender expression, sexual orientation, age, physical disability, mental disability, marital status, or any other classification protected by applicable local, state or federal laws.

Engineering

| Job listing | Job location |

|---|---|

| Planning and Systems Specialist | Penang, Malaysia |

| Process Engineer | Ithaca, New York |

| Senior Equipment Engineer | Ithaca, New York |

| Supply Chain Manager | Penang, Malaysia |

Facilities

| Job listing | Job location |

|---|---|

| Director, Global Facilities | San Jose, California |

Finance

| Job listing | Job location |

|---|---|

| Accountant | Penang, Malaysia |

| Senior Accounting Financial Analyst | San Jose, California |

Human Resources

| Job listing | Job location |

|---|---|

| Director / Senior HR Business Partner | San Jose, California |

IC Design Engineering

| Job listing | Job location |

|---|---|

| Digital IC Design Engineer | Cambridge, United Kingdom |

| Staff Digital IC Design Engineer | Cambridge, United Kingdom |

| Staff Digital IC Verification Engineer | Cambridge, United Kingdom |

Marketing

| Job listing | Job location |

|---|---|

| Head of Datacenter & Compute Business Unit | San Jose, California |

| Head of GtM Enablement | San Jose, California |

Operations

| Job listing | Job location |

|---|---|

| Direct Procurement Specialist | Penang, Malaysia |

| Indirect Procurement Specialist | Penang, Malaysia |

Package Engineering

| Job listing | Job location |

|---|---|

| Senior Packaging Engineer | Ipoh, Malaysia |

| Staff Package Development Engineer | Pasig City, Philippines |

| Staff Package Engineer | Penang, Malaysia |

Product Development

| Job listing | Job location |

|---|---|

| Manager, Product Development | Biel, Switzerland |

Product Engineering

| Job listing | Job location |

|---|---|

| Senior Product Engineer | Penang, Malaysia |

| Staff Product Engineer | Ipoh, Malaysia |

| Staff Product Engineer | Penang, Malaysia |

Quality Assurance

| Job listing | Job location |

|---|---|

| Product Quality Engineering Manager | San Jose, California |

| Supplier Quality Engineer (Fab) | Penang, Malaysia |

| Supplier Quality Engineer (OSAT) | Penang, Malaysia |

| Supplier Quality Manager | Penang, Malaysia |

Sales

| Job listing | Job location |

|---|---|

| Associate Field Applications Engineer | San Jose, California |

| Field Applications Engineer | Vasanthanagar , Bangalore |

| Field Applications Engineer | New Delhi, India |

| Senior Field Applications Engineer | Shanghai, China |

| Senior Field Sales Manager - India North | New Delhi, India |

| Staff Field Applications Engineer | San Jose, California |

Test Engineering

| Job listing | Job location |

|---|---|

| Senior Test Engineer | Pasig City, Philippines |

| Senior Test Engineer (High Power) | Penang, Malaysia |

| Staff Test Engineer | Pasig City, Philippines |

If you don't see a role that fits your profile, then apply with our General Application.

Check on an application you've submitted.

Sign up for Job Alerts.